上拉電阻和下拉電阻有什么用?

1、提高驅動能力:

例如,用單片機輸出高電平,但由于后續電路的影響,輸出的高電平不高,就是達不到VCC,影響電路工作。所以要接上拉電阻。下拉電阻情況相反,讓單片機引腳輸出低電平,結果由于后續電路影響輸出的低電平達不到GND,所以接個下拉電阻。

2、鉗位

上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平

在單片機引腳電平不定的時候,讓后面有一個穩定的電平:

例如上面接下拉電阻的情況下,在單片機剛上電的時候,電平是不定的,還有就是如果你連接的單片機在上電以后,單片機引腳是輸入引腳而不是輸出引腳,那這時候的單片機電平也是不定的,下拉電阻的作用就是如果前面的單片機引腳電平不定的話,強制讓電平保持在低電平。

3、 提高輸出的高電平值

例如: 當TTL電路驅動CMOS電路時,如果電路輸出的高電平低于CMOS電路的最低高電平(一般為3.5V), 這時就需要在TTL 的輸出端接上拉電阻,以提高輸出高電平的值

此外還有以下作用:

1、提高總線的抗電磁干擾能力,管腳懸空就比較容易接受外界的電磁干擾;

2、長線傳輸中電阻不匹配容易引起反射波干擾,加上、下拉電阻是電阻匹配,有效的抑制反射波干擾。

3、 如果電平用OC(集電極開路,TTL)或OD(漏極開路,CMOS)輸出,那么不用上拉電阻是不能工作的, 這個很容易理解,管子沒有電源就不能輸出高電平了。

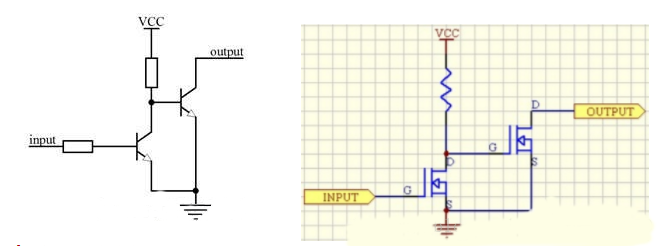

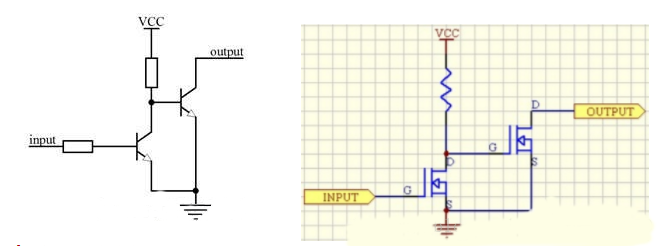

如下圖所示:

集電極開路輸出的結構如圖1所示,右邊的那個三極管集電極什么都不接,所以叫做集電極開路;和集電極開路類似,漏極開路輸出;

一般情況下都需要在OUTPUT 輸出口 外接上拉電阻,才能輸出高電平。否則在右邊三極管截止時,輸出的是高阻態。

高阻態狀態下便于多個三極管并聯(線與邏輯) 有一個為低電平,所有的都為低電平。

上下拉使用對比:

需要注意的是,上拉電阻太大會引起輸出電平的延遲。(RC延時)一般CMOS門電路輸出不能給它懸空,都是接上拉電阻設定成高電平。

下拉電阻:和上拉電阻的原理差不多, 只是拉到GND去而已。 那樣電平就會被拉低。 下拉電阻一般用于設定低電平或者是阻抗匹配(終端端接)。

上拉是對器件輸入電流,下拉是輸出電流;

上拉用來增大電流,下拉電阻是用來吸收電流。

選用原則:

上拉電阻阻值的選擇原則包括:

1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。

2、從確保足夠的驅動電流考慮應當足夠小;電阻小,電流大。

3、對于高速電路,過大的上拉電阻可能邊沿變平緩。

綜合考慮以上三點,通常在1k到10k之間選取。對下拉電阻也有類似道理

上拉電阻偏大或偏小的影響: 400kbs

上拉電阻值過小,Vcc灌入端口的電流(Ic)將較大,這樣會導致MOS管V2(三極管)不完全導通(Ib*β,有飽和狀態變成放大狀態,這樣端口輸出的低電平值增大(i2c協議規定,端口輸出低電平的最高允許值為0.4v)。

如果上拉電阻過大,加上線上的總線電容,由于RC影響,會帶來上升時間的增大(下降延是芯片內的晶體管,是有源驅動,速度較快;上升延是無源的外接電阻,速度慢),而且上拉電阻過大,即引起輸出阻抗的增大,當輸出阻抗和負載的阻抗可以比擬的時,則輸出的高電平會分壓而減少。

低功耗狀態 上拉下拉使用注意:

帶上拉或者下拉的IO口,在低功耗狀態,或者配置使用的常態時,應根據IO口的狀態進行相關的設置。

如果IO口沒有做好處理的話,它就會在暗地里偷走功耗,而你卻渾然不知。具體原因是這樣的,一般的IO的內部或者外部都會有上下拉電阻,舉個例子,如下圖所示,假如某個IO口有個10KΩ的上拉電阻,把引腳拉到3.3V,然而當MCU進入低功耗模式的時候,此IO口被設置成輸出低電平,根據歐姆定律,此引腳就會消耗3.3V/10K=0.33mA的電流,假如有四、五個這樣的IO口,那么幾個mA就貼進去了,太可惜了。所以在進入低功耗之前,請逐個檢查IO口的狀態:

如果此IO口帶上拉,請設置為高電平輸出或者高阻態輸入;

如果此IO口帶下拉,請設置為低電平輸出或者高阻態輸入;

總之一句話,不要把上好的電流浪費在產生熱量的功能上,咱可不靠這點溫度去暖手。

IO口上拉與下拉電平與IC間的連接造成的相應功耗的損失:

IO口的上下拉電阻消耗電流這一因素相對比較明顯,下邊咱來說一個不明顯的因素:IO口與外部IC相連時的電流消耗。假如某個IO口自帶上拉,而此與IO相連的IC引腳偏偏是自帶下拉的,那么無論這個引腳處于什么樣的電平輸出,都不可避免的產生一定的電流消耗。所以凡是遇見這一類的情況,首先需要閱讀外設IC的手冊,確定好此引腳的的狀態,做到心中有數;然后在控制MCU睡眠之前,設置好MCU的IO口的上下拉模式及輸入輸出狀態,要保證一絲兒電流都不要被它消耗掉。

系統功耗測試。

檢測出來的電流消耗很大,可實際應用消耗的功耗卻不大?

是因為在測試功耗的時候MCU還連接著調試器呢!這時候大部分電流就會被調試器給擄走,平白無故的讓工程師產生極度郁悶的心情。所以在測低功耗的時候,一定不要連接調試器,更不能邊調試邊測電流。

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹